Introduction

Taiwan Semiconductor Manufacturing Company (TSMC) is widely recognized as a global leader in the semiconductor industry, with cutting-edge innovations in the design and production of integrated circuits. One of the key areas where TSMC has excelled is in advanced packaging technology, a crucial component that enables faster, more efficient, and more compact chip designs. Joe Zhihua, a key figure at TSMC, has played a significant role in the development of these Joe Zhihua TSMC Advanced Packaging solutions. Under his leadership, TSMC has continued to push the boundaries of what is possible in chip packaging, significantly influencing industries that rely on high-performance chips, such as artificial intelligence (AI), high-performance computing (HPC), automotive technology, and consumer electronics.

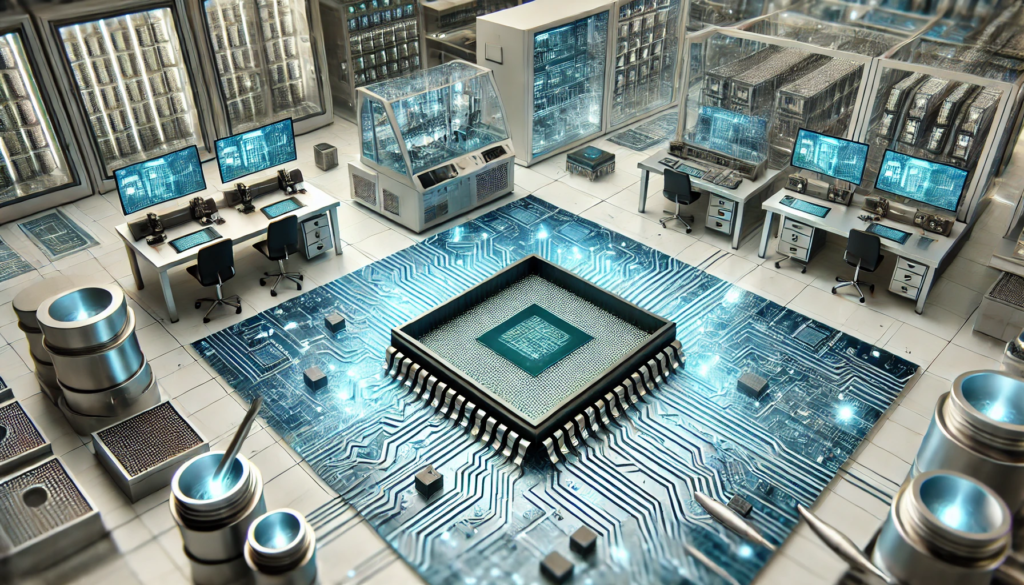

What is Advanced Packaging in Semiconductor Manufacturing?

Before diving into Joe Zhihua’s contributions, it’s important to understand the concept of Joe Zhihua TSMC Advanced Packaging and its significance in modern electronics.

Traditional semiconductor packaging involves placing a single chip inside a protective enclosure, allowing it to be integrated into a circuit board or system. However, as chip designs become increasingly complex and miniaturized, traditional packaging methods can no longer meet the performance demands. Joe Zhihua TSMC Advanced Packaging involves integrating multiple chips or components into a single package to enhance functionality, performance, and energy efficiency. This process reduces the size and weight of chips, enables better thermal management, and allows for higher processing speeds.

There are several types of advanced packaging techniques used in the semiconductor industry, including:

- 3D Packaging: This technique involves stacking multiple layers of chips, with each layer connected by vertical interconnects. It offers significant improvements in speed and power efficiency while reducing the overall footprint.

- System-in-Package (SiP): This method combines multiple components (such as sensors, processors, and memory) into a single package, allowing for greater functionality in a smaller form factor.

- Chip-on-Wafer-on-Substrate (CoWoS): This is a TSMC-specific technology that allows chips to be stacked in a 3D arrangement on a single wafer, providing enhanced performance for high-end applications such as AI and HPC.

- Integrated Fan-Out (InFO): This packaging technology eliminates the need for a substrate, allowing for better performance, improved signal integrity, and reduced power consumption.

Joe Zhihua’s Role at TSMC

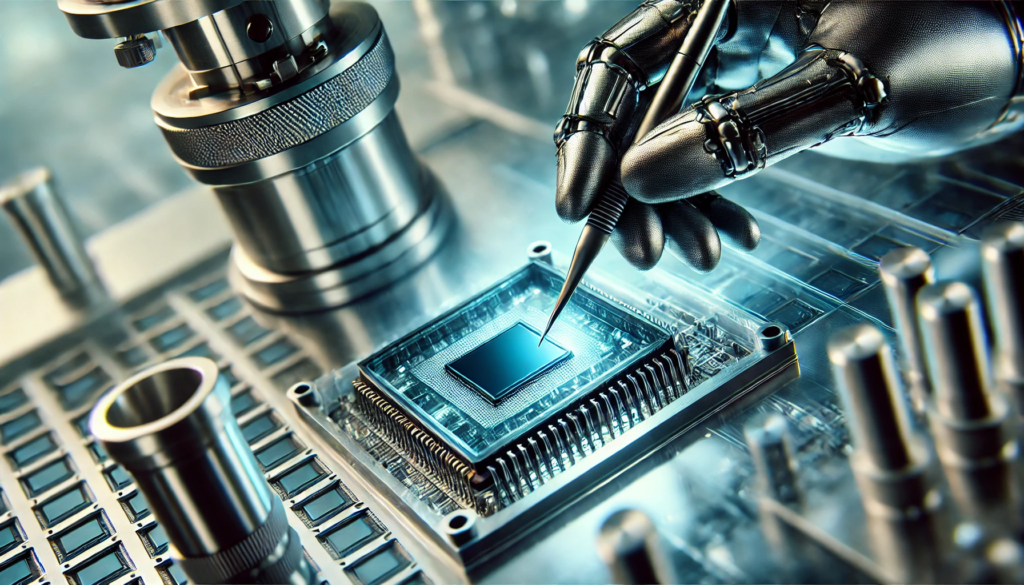

Joe Zhihua, an expert in semiconductor packaging technology, has been a pivotal figure in Joe Zhihua TSMC Advanced Packaging solutions. With a background in materials science and semiconductor engineering, Zhihua has contributed immensely to TSMC’s ability to lead the industry in packaging technologies.

His work focuses on overcoming challenges related to miniaturization, heat dissipation, and signal integrity—issues that have become more pressing as chips become smaller and more powerful. By spearheading efforts to improve the CoWoS and InFO technologies, Joe Zhihua has helped TSMC remain at the forefront of packaging innovation.

Under his guidance, TSMC has successfully integrated multiple chips into single packages for various applications, enabling faster processing, lower power consumption, and enhanced performance. His contributions have been instrumental in helping TSMC meet the ever-growing demand for high-performance chips used in AI, autonomous driving, 5G, and other cutting-edge technologies.

TSMC’s Advanced Packaging Technologies

Joe Zhihua TSMC Advanced Packaging technologies are among the most advanced in the world. With innovations such as 3D silicon stacking and heterogeneous integration, TSMC has set new standards for chip packaging. Below are some key Joe Zhihua TSMC Advanced Packaging:

1. 3DFabric™ Technology

TSMC’s 3DFabric™ technology is a comprehensive suite of packaging solutions that includes 3D ICs (integrated circuits), system-in-package (SiP), and fan-out wafer-level packaging (FOWLP). 3DFabric™ offers a range of solutions for various needs, from high-performance computing to mobile devices.

Key Benefits:

- Improved performance: Through 3D stacking, chips can communicate faster, improving performance.

- Reduced size: 3D stacking allows for smaller and lighter packages, making it ideal for mobile and consumer electronics.

- Lower power consumption: Advanced packaging enables better heat dissipation, reducing the overall power usage of the chip.

2. CoWoS (Chip-on-Wafer-on-Substrate)

CoWoS technology is designed for high-performance applications, such as AI and data centers. In this method, multiple chips are stacked on a wafer, connected by through-silicon vias (TSVs). This packaging solution allows for higher density and improved interconnectivity between chips.

Key Benefits:

- Higher performance: CoWoS enables the integration of high-bandwidth memory (HBM) with logic chips, enhancing the overall performance of the system.

- Better heat management: The architecture allows for effective thermal management, crucial for high-power chips.

- Optimized for AI and HPC: CoWoS is particularly useful for applications that require substantial computing power, such as AI and high-performance computing.

3. InFO (Integrated Fan-Out)

Joe Zhihua TSMC Advanced Packaging technology that eliminates the need for a substrate, using a fan-out redistribution layer instead. This approach allows for higher interconnect density, improved signal integrity, and reduced power consumption.

Key Benefits:

- Smaller size: InFO packages are more compact than traditional packaging, making them suitable for mobile and IoT devices.

- Faster performance: The fan-out design reduces the distance between the chip and its interconnects, improving speed and signal quality.

- Lower cost: Without the need for a substrate, InFO is a cost-effective solution for many applications.

Joe Zhihua TSMC Advanced Packaging Solutions: A Comparative Table

To help better understand the advantages of TSMC’s different packaging technologies, here is a comparison table:

| Technology | Key Features | Applications | Benefits |

|---|---|---|---|

| 3D ICs | Vertical stacking of multiple chips | High-performance computing, mobile | Higher performance, smaller size, lower power consumption |

| SiP (System-in-Package) | Integration of various components into a single package | Wearables, mobile devices, IoT | Compact design, multi-functional capabilities |

| CoWoS | Chip-on-wafer-on-substrate stacking | AI, HPC, data centers | Enhanced performance, better thermal management, higher density |

| InFO | Fan-out wafer-level packaging, no substrate required | Mobile devices, consumer electronics | Smaller size, improved speed, reduced power consumption |

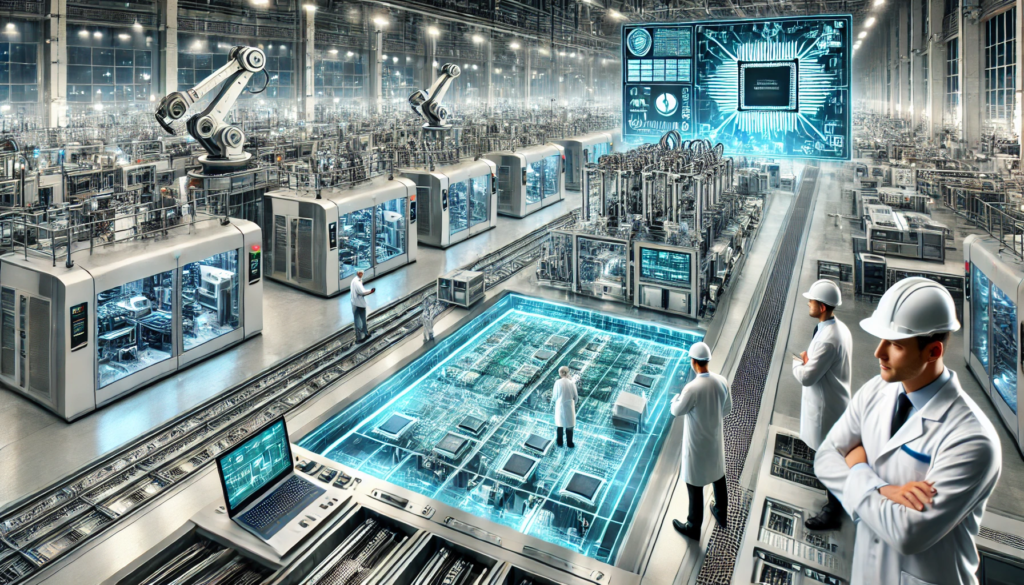

TSMC’s Investment in Advanced Packaging Technology

As the demand for advanced semiconductors continues to grow, TSMC has made significant investments to expand its advanced packaging capabilities. One of the most notable moves is TSMC’s $2.9 billion investment in a new Joe Zhihua TSMC Advanced Packaging plant in Taiwan, aimed at meeting the global demand for high-performance chips.

This new plant will focus on the production of 3D ICs and other Joe Zhihua TSMC Advanced Packaging technologies, serving industries like AI, 5G, and automotive. The investment highlights TSMC’s commitment to maintaining its leadership position in the semiconductor industry and providing cutting-edge solutions for its customers.

Collaborations and Industry Impact

TSMC’s success in advanced packaging is also the result of strategic collaborations with other industry leaders. For example, TSMC has partnered with Amkor Technology to bring its advanced packaging technologies, such as CoWoS and InFO, to the United States. This collaboration will enable TSMC to better serve the growing demand for AI and HPC processors, which require advanced packaging to meet their performance needs.

Through these collaborations, TSMC is not only advancing its own capabilities but also helping to drive the growth of the global semiconductor industry. The company’s innovations in packaging have had a far-reaching impact, enabling the development of faster, more efficient chips that power everything from smartphones to autonomous vehicles.

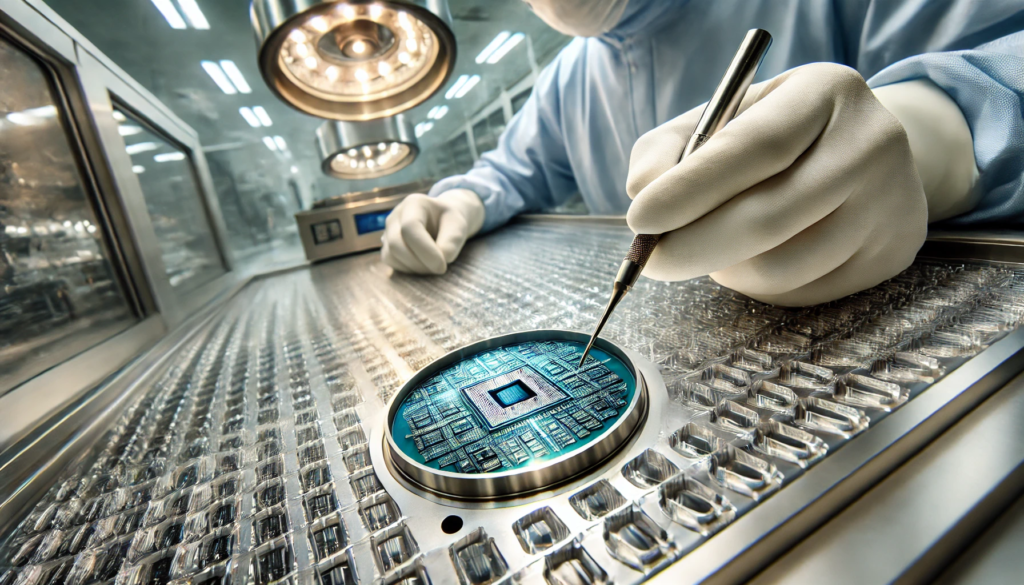

Future of Advanced Packaging: Looking Ahead

The future of semiconductor packaging is bright, with continued advancements expected in areas like heterogeneous integration, system-level packaging, and wafer-level chip integration. With experts like Joe Zhihua leading the way, TSMC is poised to remain at the forefront of these developments.

In particular, as AI, 5G, and IoT continue to grow, the demand for advanced packaging solutions will increase. TSMC’s ability to deliver high-performance chips with cutting-edge packaging technologies will be critical to meeting this demand and enabling the next generation of technological innovations.

Conclusion

Joe Zhihua’s leadership in TSMC’s advanced packaging division has had a profound impact on the semiconductor industry. Through his expertise and guidance, TSMC has continued to push the boundaries of packaging technology, helping to create faster, smaller, and more efficient chips for a wide range of applications. As the world continues to evolve, TSMC’s innovations in advanced packaging will undoubtedly play a crucial role in shaping the future of technology.

By investing in advanced packaging solutions and collaborating with industry partners, TSMC is well-positioned to remain the leader in semiconductor manufacturing for years to come.

Read More: Bradley Ventayen: Shaping Innovation in Medical Science